Тренды разработки FPGA-отладок в 2020г

О том, когда размер имеет значение

Тренд сегодня

Какой-то тренд в последнее время на выпуск мини-, мико- и даже нано-плат для FPGA, моду тут задал ICEstick от Lattice, но неужели эволюция нас отбросила обратно в нулевые, когда мужчины мерялись телефонами (у кого меньше) ?!..

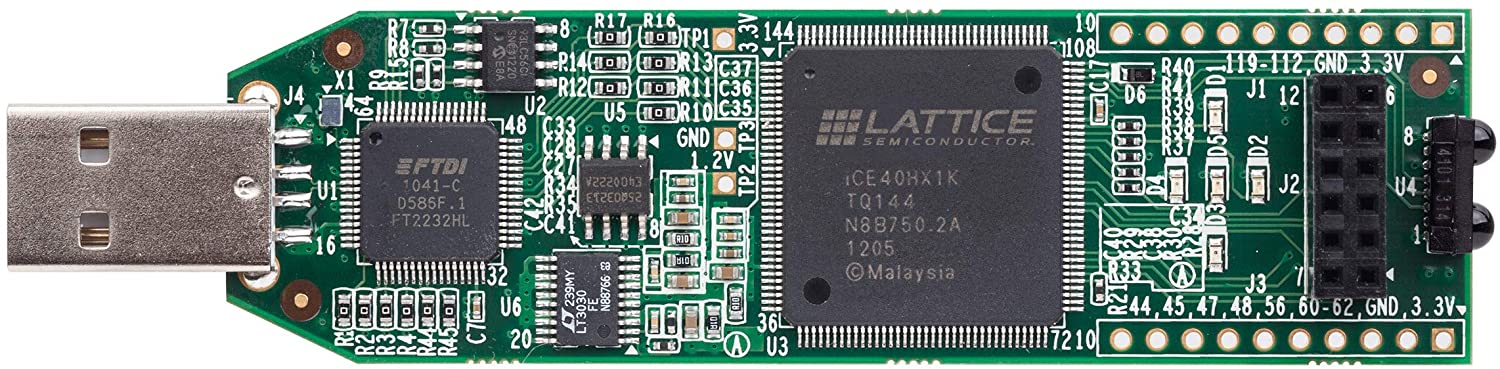

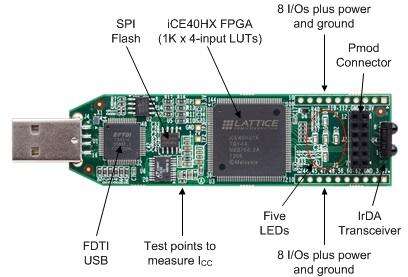

В случае ICEstick размер был объясним: плата за $20 (ниже себестоимости!) была отличным маркетинговым ходом, некоей заманухой, предлагающей на эвалюэйшен свежую ПЛИС от свежеприобретенной SiliconBlue. Экономили как могли, но доступный стик выпустили (даже впаяли USB-A, чтобы не комплектовать плату доп.кабелем).

Однако, в случае разработок энтузиастов, которые сегодня появляются как грибы после дождя для меня совершенно необъяснима экономия такого дешевого материала как текстолит.

Нет, конечно для entry-level энтузиастов эти платы верх мечтаний: помигать светодиодом или даже вывести на него ШИМ и всё в этом роде с лихвой покрывается возможностями плат, но… не более того. Спасибо хоть на некоторых платах есть PMOD - стандантизированный дижилентом порт расширения для подключения своей периферии, но только единицы ставят его.

Собственно это был плач о том, почему же на отладки для ПЛИС не насыпят по максимуму ресурсов I/O, да еще и используют стандартизированные порты для расширения, а уж о таких вещах как PCI-E, хотя бы в М.2 исполнении (раз уж всё равно ставят ЕСР5) даже и мечтать страшно.

Иллюстрация того как делают сейчас

Собственно вот тот самый законодатель мод на мини-отладки от вендоров: ICEstick от LatticeSemi:

Ниже - можные сегодня мини-, мико- и нано-платы для FPGA.

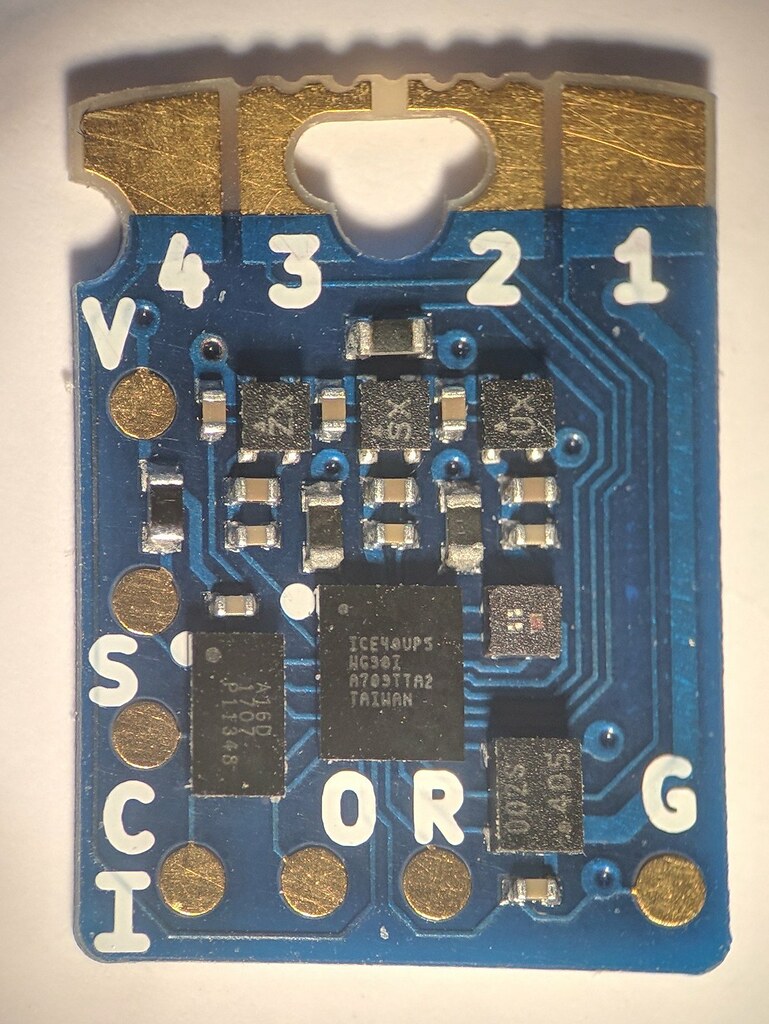

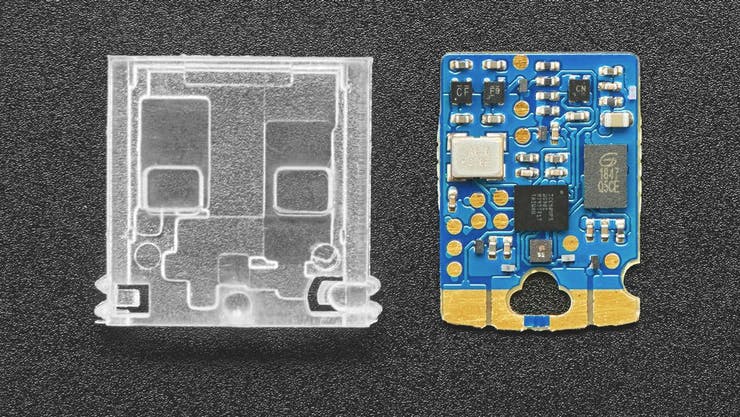

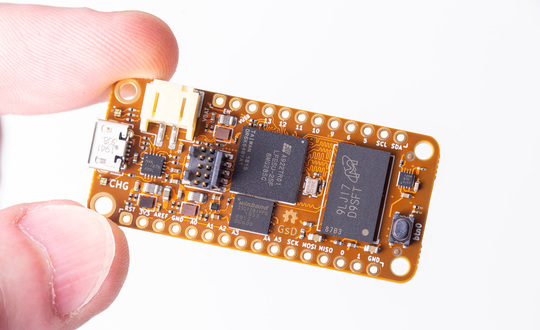

FOMU

ICE40UP5K

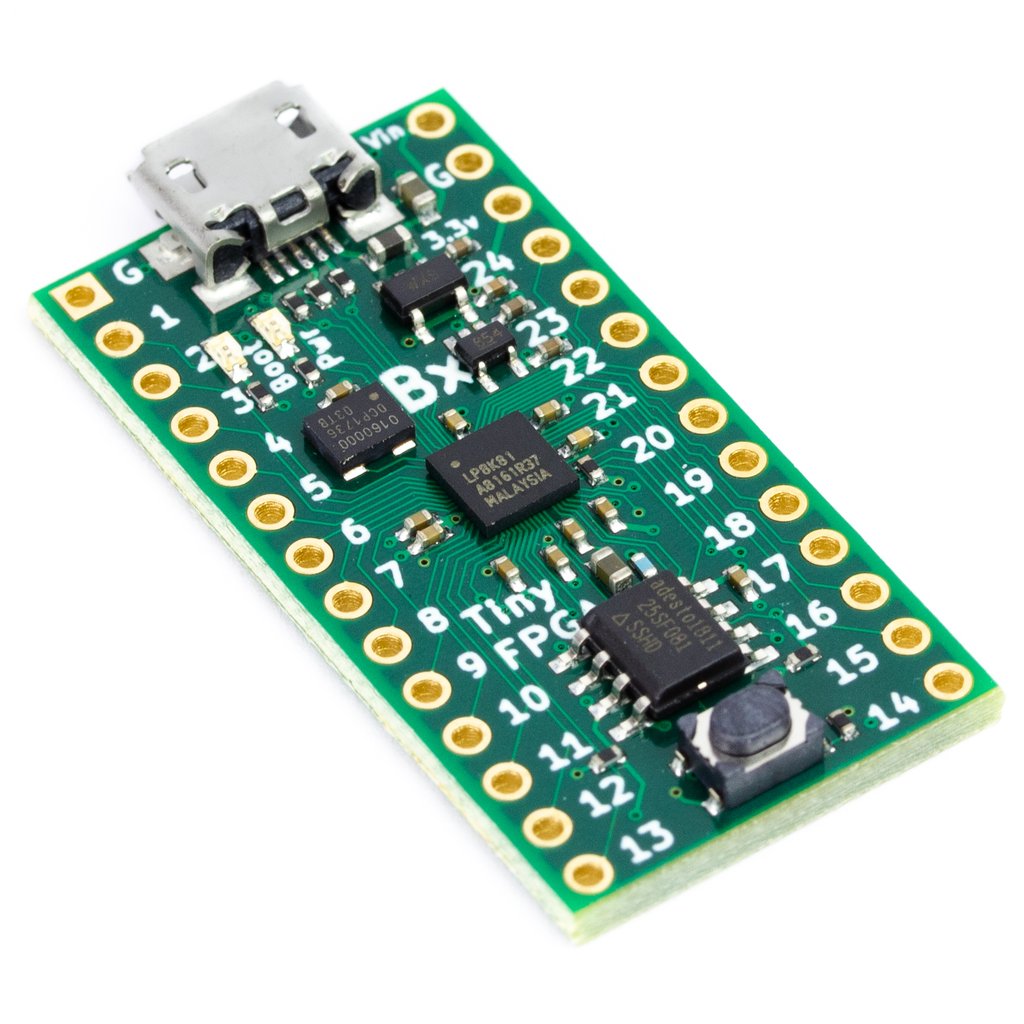

TinyFPGA

WebFPGA

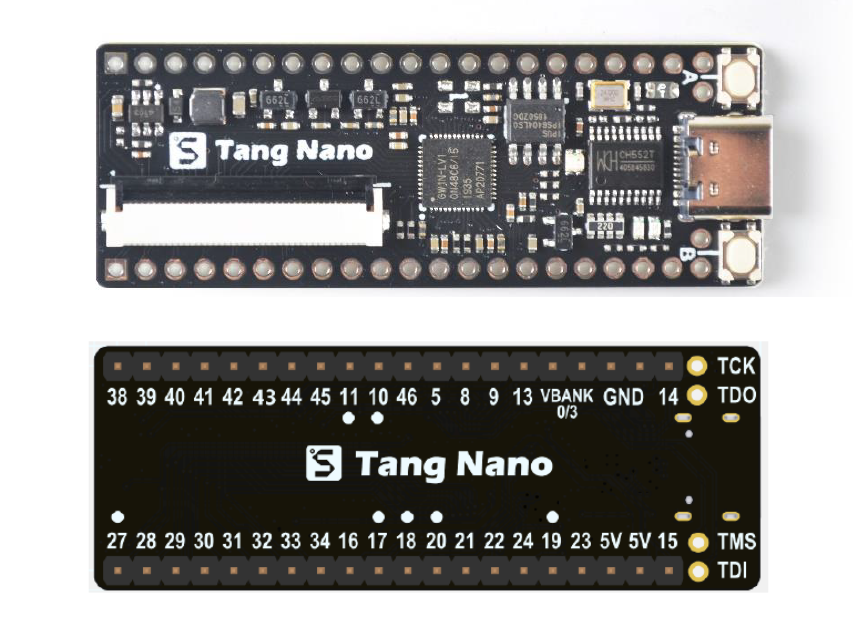

Sipeed TANG NANO

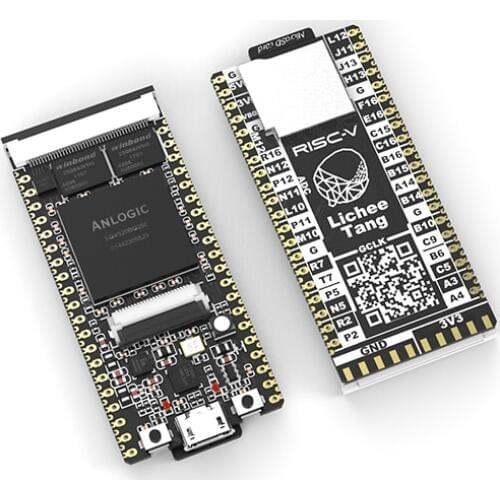

Sipeed TANG PRIMER

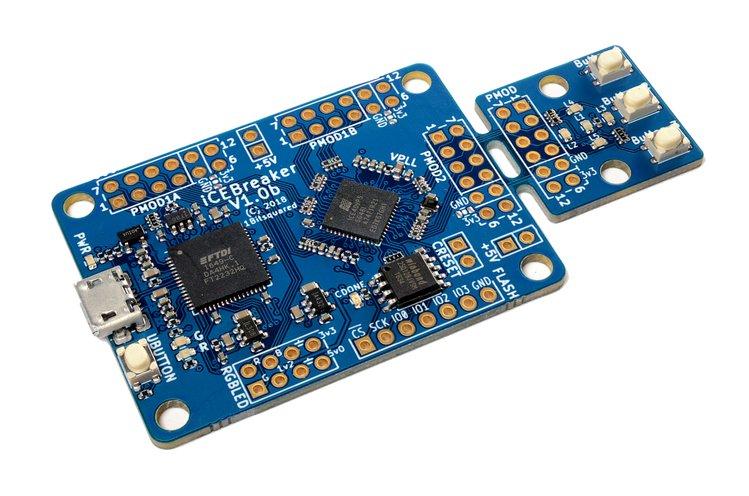

ICEbreaker

ICE40UP5K

OrangeCrab

ECP5 LFE5U-25F

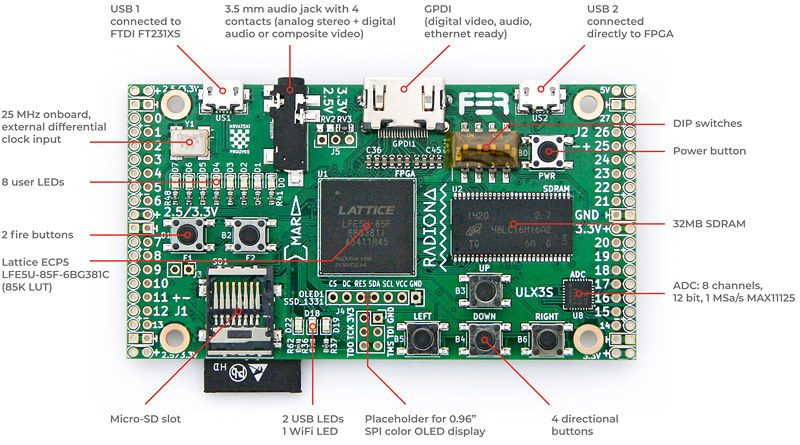

ULX3S

ECP5 LFE5U-85F

FPGA плата моей мечты

Собственно, а чего хотелось бы от FPGA платы? Помимо возможности доступа к максимуму ресурсов I/O и стандартизированным портам расширения периферии?

Также важным пунктом является наличие набортного JTAG-адаптера и USB-to-UART, а если этим UART (через вспомогательные линии) можно учинять ресет платы (всей или только FPGA-части) - то разработчик такой платы сразу получит статус “золотые руки” (Mojo V3 была очень близка к этому идеалу)

Пожалуй, это всё, с той лишь оговоркой, что стандарт расширения периферии должен быть “дешевым” и “удобным”, т.е. всякие FMC и SYZYGY отпадают сразу. Под удобством тут понимается возможность подключения NAND FLASH или какого-нить гипотетического FT601 без каких-либо проблем и велосипедостроения: здесь, увы, отваливается и PMOD.

Основной поинт в контексте поста про миниатюризацию отладок для энтузиастов: выкиньте с платы по максимуму ненужной периферии, тем самым уменьшив стоимость и позвольте пользователю расширять самому по максимуму (насколько это позволяет ПЛИС) функционал за счёт приобретения (нужных ему) “допов”, и совсем здорово, если эти допы можно будет использовать на других отладках.

Bonus

По поводу таких вещей как PCI-E и в целом о доступе к MGT трансиверам на тех чипах, где они имеются, вот такая мега-идея: выводим на USB3/USB-C коннекторы (в них, если надо, и для входного диф.клока найдутся пара лишних линий), а дальше хоть майнеровскими райзерами в хост на PCI-E прокидываем.