Содержание

Блеск и нищета современных генераторов карты регистров для VLSI

Make CSR generators useful again!

Генераторы RTL карты регистров (или CSR - control/status registers) появились задолго до стандарта IP-XACT, а значит прошли достаточно большой путь эволюции. Да и сам IP-XACT за это время "эволюционировал" в SystemRDL.

Однако до сих пор существуют детские проблемы, а то и вовсе фундаментальные недоработки тулов для генерации RTL CSR.

Далее по пунктам разберу что же с ними не так?

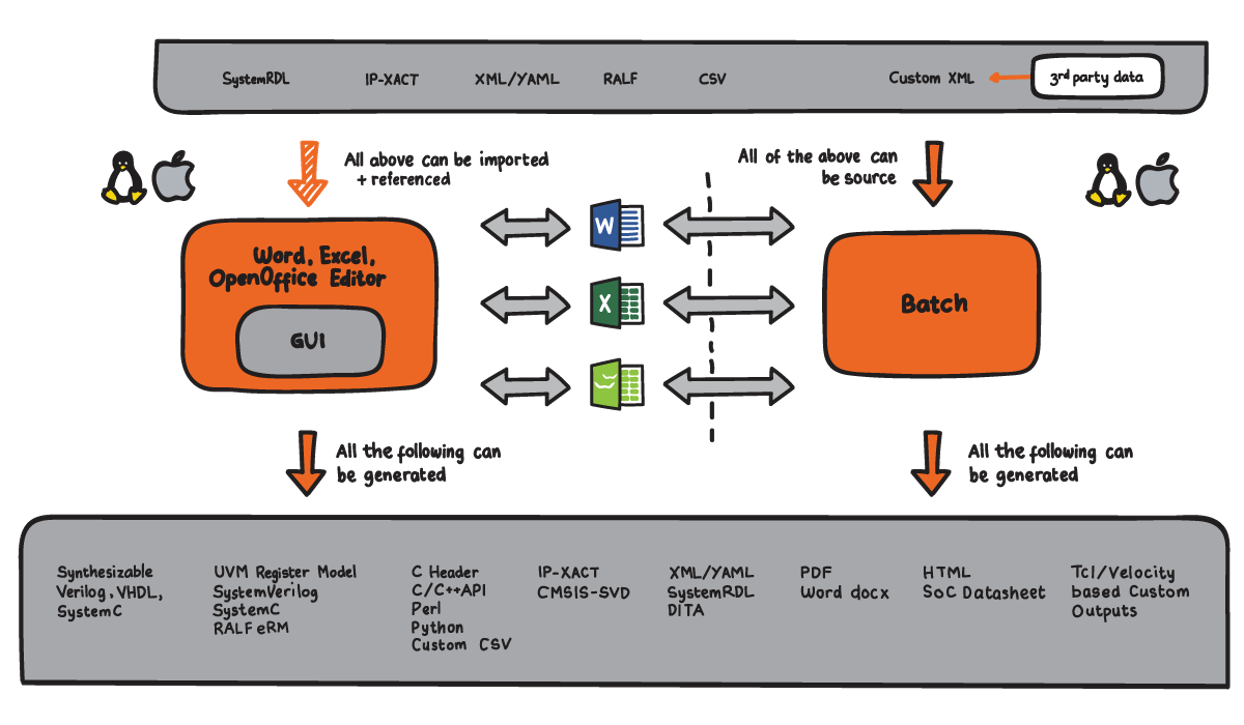

1. Zoo and lack of Standards supports

Это конечно прозвучит весьма странно, однако даже сегодня не у всех тулов есть поддержка IP-XACT & SystemRDL.

Окей. Если тулы не поддерживают стандарт, значит у них есть собственный уникальный взгляд на метаописание карты регистров. Приемлемо, но… помимо зоопарка форматов на метаописание присутствует крайне неприятная вещь в виде зоопарка в описании полей доступа - и тут возникает достаточно нетривиальная задача по матчингу разных типов между разными тулами.

Более того в некоторых метаописаниях предусматривается несколько полей доступа, например у SystemRDL их два: для HW и SW доступа, что лишь плодлливает масла в огонь.

2. SV only, not Verilog

Есть определенная категория тулов, которая поддерживает RTL-вывод только в VHDL. Однако большая часть тулов поддерживает RTL-вывод в SystemVerilog и VHDL. Pure Verilog в пролёте.

Т.е. я понимаю что систем-верилог - это модно, стильно, молодёжно, но такая оголтелая ориентация на SV как на основной RTL deliverables, а не на Verilog.. Сириусли?

Т.е. по замыслу разработчиков опен-сорс тулов для генерации карты регистров у вас нет денег на покупку коммерческого тула для генерации карты регистров, но есть деньги на покупку синтезатора и симулятора от $SNPS/$CDNS ??? Смехотворно!

3. Registers splitting mechanism

Довольно распространённый сценарий, но я почему-то не смог найти поддержку его реализации у текущих тулов. Имею в виду кейс, когда ширина регистра/поля регистра превосходит ширину внутренней шины данных.

Вот допустим есть переменная value7[19:0], а доступ к шине данных - восьмибитный, т.о. надо переменную расположить в трёх соседних ячейках:

-

value7[19:16] -

value7[15:8] -

value7[7:0]

Т.е. гипотетический workaround понятен: можно описать регистр как три отдельных регистра с идентичным именем, но разными диапазонами бит, но в этом случае атрибуты и описание регистра надо будет продублировать дважды, что как-то не особо методологически правильно.

Другой пример: [записать|прочитать] [ключ|результат] шифрования размером 128 или 256 бит по шине 32-битного процессора.

4. Documentation as last priority

Такое ощущение, что генераторы полей регистров ориентированы на всё что угодно, но не на автоматическое формирование документации следуя концепции единого источника.

Основные претензии:

-

До сих пор нету красивой рисовалки полей регистров. Если таковой функционал заявлен, то реализуется через

bitfield(форк автора Wavedrom)либо с помощью ПО из набораasciidoctor-diagrams. -

Нет достаточного числа полей для описания функционала регистра/поля регистра, чтобы в автоматическом режиме сгенерировать исчерпывающую документацию. В идеале хотелось бы иметь следующие поля для документации в метаописании:

-

Имя для машины (название переменной в коде)

-

Имя для человека (человекопонятное имя сущности)

-

Описание (для таблицы регистров)

-

Расширенное описание (в том случае, если описание функционала довольно объёмное, то его можно вынести в отдельный абзац с помощью расширенного описания)

-

-

Не все тулы поддерживают многострочные строки (с возможностью произвольного форматирования внутри такой строки): хотелось бы иметь возможность прям в метаописании применять специфичное для документации форматирование (asciidoc/markdown разметку), которые 1-в-1 будут вставляться в документ при рендере. В этом плане весьма выигрышны метаописания на основе формата Yaml, который нативно поддерживает подобные многострочные описания.

5. Configurations' support

Ну и на десерт самое экзотичное.

Для документации и автоматической генерации системных/функциональных тестов очень хочется реализации поддержки неких сетапов/конфигов, которые по сути содержат описания инициализационной последовательности для разных кейсов.

Вот, допустим, есть универсальный IP-блок: USB. И этот блок можно сконфигурировать как Host или как Device. Т.е. помимо значений по сбросу для полей регистров, метаописание будет иметь еще два значения на каждое поле: сценарий#1 (Host) и сценарий#2 (Device). В каких-то случаях (там где это необходимо) необходимо помимо самих значениях полей для сценария указывать еще и последовательность инициализации полей регистров: порядковым номером (если каждое поле должно быть проинициализировано в строгом порядке) или указанием зависимостей after и before от проинициализированных полей.

Помимо автоматической генерации документации с описанием сценариев работы и конфигурации, можно теже сценарии использовать для верификаци для быстрой настройки на определенный режим работы и для генерации Си-кода с последовательностью инициализации (для системных тестов или end user сценариев применения).

Links for open-sourced CSR Reg Map generators

-

PeakRDL :: (Python) Control and status register code generator toolchain

-

reggen and regtool :: (Python) from OpenTitan project

-

RGGEN :: (Ruby) Code generation tool for control and status registers

-

Corsair :: (Python) Control and Status Register map generator for HDL projects

-

Cheby :: (Python) aims at defining a file format to describe the HW/SW interface (the memory map), and a set of tools to generate HDL, drivers, documentation. Publication