Аннотация

Для тех кто давно в теме FPG/A/SIC или просто по работе/хобби связан с проектированием на ПЛИС (или СБИС) удобно под рукой иметь агрегатор полезностей и советов, чем тратить время на самостоятельный сёрфинг по LinkedIn/Twitter/WikiChip/SemiWiki/etc..

В качестве инициативы, сделали с единомышленниками пару каналов для агрегации интересных проектов и полезных советов (из собственной проектной практики и из сети). Детали о каналах ниже.

IP-cores

Пополняемая коллекция СФ-блоков на языках Verilog/VHDL для реализации на ПЛИС/СБИС. Подавляющее большинство блоков — опенсорсные и допускающие свободное использование. Помимо СФ-блоков периферии и интерфейсов есть процессорные ядра (розлива таких пивзаводов как MIPSopen, RISC-V, etc) а также отдельный класс библиотек примитивов (в том числе для упрощения кросдоменных переходов) и алгоритмические ядра (ЦОС, нахождение и коррекция ошибок с CRC/ECC).

Что уже можно найти в канале по периферийным IP-ядрам:

- DisplayPort, HDMI, DVI, VGA

- HMC (Hybrid Memory Cube)

- DDR3 controller

- PCI-E + DMA engine

- Interconnect core, NoC

- Bridges to FX2LP (CY7C68013), FX3, FT2232

- AXI buses (itself + Bus Functional Model + Assertions)

- PonyLink

- HyperBUS

- USB2 (ULPI)

- USB3 (PIPE),

- RNG, TRNG

- Cryptography cores: hashes, stream ciphers, assymetric ciphers

- MIPI DSI, MIPI CSI

- HyperRAM

- и т.д. и т.п.…

Язык канала — английский, организован удобный поиск по #хештегам (язык, тип СФ-блока/периферии, вендор ПЛИС (если применимо)).

- Адрес: telegram:ipcores

- Альтернативный адрес: t.me/ipcores

FPG[A]SIC

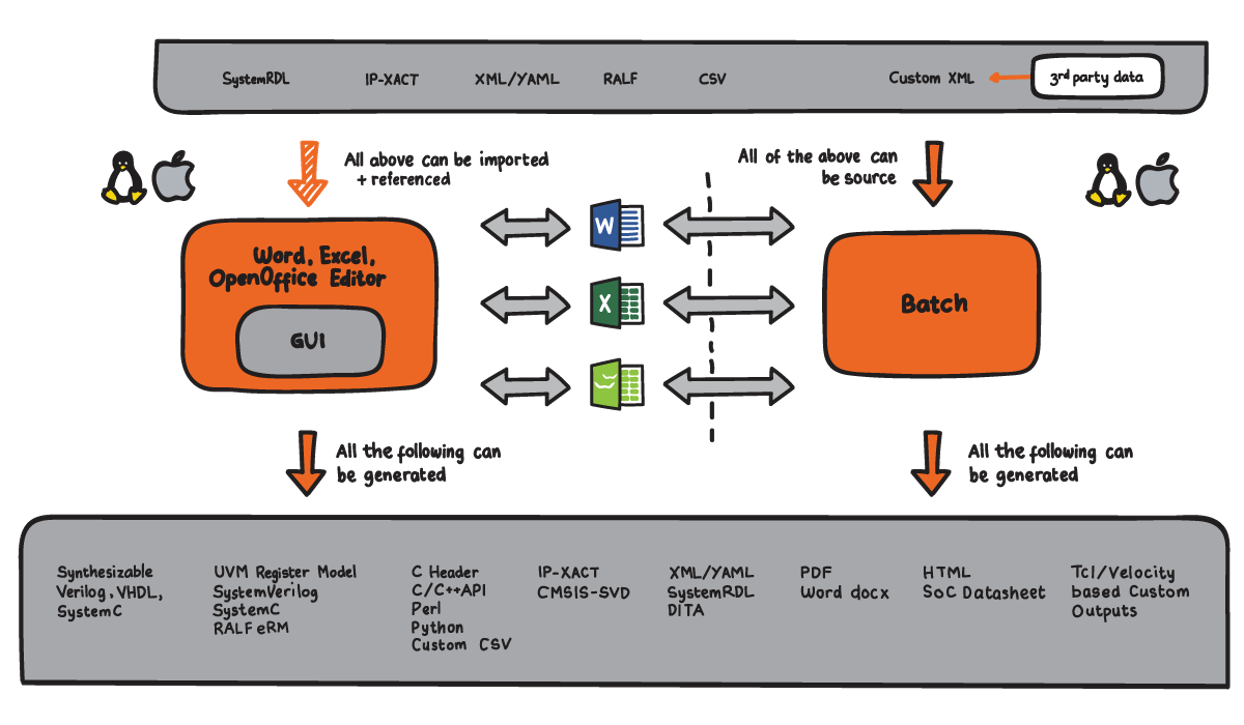

Основная направленность канала — Design Automation, т.е. отказ от GUI в пользу скриптов для автоматизации рутинных действий,

Помимо этого в канале сейчас можно найти полезную информацию по таким темам как: полезные советы по EDA-инструментарию (Cadence/Synopsys, Vivado, Quartus, Yosys, ICEstorm, Verilator, Icarus Verilog, etc), примеры скриптов для автоматизации EDA, трюки по использованию специфичных tcl-команд, недокументированные/малоизвестные возможности тулов, HLS (High level synthesis) инструментарий с открытыми исходными кодами, NN/ML-фрейворки (нейросети и машинное обучение) для ПЛИС, скрипты автоматической сборки datasheets, подходы к использованию свободного инструментария формальной верификации, надстройки и плагины HDL для текстовых редакторов и IDE, свободные книги по тематике FPGA и HDL, советы по настройке Lint’еров, тонкости версионирования в git проектов FPGA & ASIC, трюки по сведению таймингов (лучшии выжимки из Ultrafast Methodology), реверсинжиниринг ПЛИС и используемых форматов представления данных (в т.ч. парсинг битстримов), свободные трансляторы Python -> HDL, продвинутые методики BROM/DSP folding/multi-pumping, подходы работы с партишинами и частичной реконфигарацией (partitions and partial recunfiguration), clock conversion and constraining, HDL tips and tricks, example to use DNA-protection, etc.

Язык канала — английский, организован удобный поиск по #хештегам (вендор ПЛИС/EDA, функционал, язык).

- Адрес: telegram:ipcores

- Альтернативный адрес: t.me/fpgasic