Приведенное ниже - описание к коллекции моих EDA-скриптов для работы с тулами для ASIC и FPGA

Конвертор из UCF в XDC

Конвертирует для ПЛИС Xilinx привязки ножек и стандартов из формата ucf (Xilinx ISE) в новый формат xdc (Xilinx Vivado). Использование:

./ucf-to-xdc.sh FILENAME.ucf

В текущей директории появится файл FILENAME.xdc.

Пример входного ucf-файла

NET "DDR_DQ[0]" LOC = "AY12" | IOSTANDARD = SSTL15_T_DCI | VCCAUX_IO = NORMAL | SLEW = FAST;

NET "DDR_DQ[1]" LOC = "AW12" | IOSTANDARD = SSTL15_T_DCI | VCCAUX_IO = NORMAL | SLEW = FAST;

Пример сгенеренного утилитой xdc-файла

set_property PACKAGE_PIN AY12 [get_ports DDR_DQ[0]]

set_property IOSTANDARD SSTL15_T_DCI [get_ports DDR_DQ[0]]

set_property VCCAUX_IO NORMAL [get_ports DDR_DQ[0]]

set_property SLEW FAST [get_ports DDR_DQ[0]]

set_property PACKAGE_PIN AW12 [get_ports DDR_DQ[1]]

set_property IOSTANDARD SSTL15_T_DCI [get_ports DDR_DQ[1]]

set_property VCCAUX_IO NORMAL [get_ports DDR_DQ[1]]

set_property SLEW FAST [get_ports DDR_DQ[1]]

Ограничения

Текущая версия парсера позиционно-зависима от порядка перечисления свойств в файле ucf. Необходимо следовать этому формату для корректной работы утилиты.

Планы

Переписать скрипт на новый однострочный формат xdc-файла:

set_property -dict {PACKAGE_PIN AY12 IOSTANDARD SSTL15_T_DCI VCCAUX_IO NORMAL SLEW FAST} [get_ports DDR_DQ[0]];

Скрипт

https://github.com/iDoka/eda-scripts/blob/master/ucf-to-xdc.sh

Мониторинг запущенных на сервере Xilinx Vivado

Скрипт находит запущенные процессы Vivado от юзера (vivado-stat-user.sh) или все процессы Vivado на сервере (vivado-stat.sh) и печатает по ним суммарную статистику: утилизацию CPU и ОЗУ. Вешь крайне полезная для ослеживания исчерпания ресурсов (особенно при синтезе под Vitrex-7 2000T).

Запуск:

./vivado-stat.sh

после чего будет запущен периодический сбор информации и вывод на экран потребляемых ресурсов. В скрипте можно подстроить параметры:

CMD- какую конкретно команду отслеживаем (можно сменить на Quartus/Lattice/whatever_you_want)PERIOD- целочисленное значение секунд, определяющее период наблюдения

Пример запуска

Пример вывода скрипта при PERIOD="30s":

$ ./vivado-stat.sh

97% 1265M

99% 1459M

98% 1570M

98% 1822M

99% 1948M

99% 2138M

99% 2531M

99% 2821M

103% 2928M

103% 3098M

428% 7092M

477% 8959M

446% 10335M

375% 10408M

435% 11391M

441% 11633M

460% 13799M

420% 13966M

404% 14006M

296% 9994M

*** vivado was finished running at 11:11 06.07.2016 ***

$

Скрипты

- https://github.com/iDoka/eda-scripts/blob/master/vivado-stat.sh

- https://github.com/iDoka/eda-scripts/blob/master/vivado-stat-user.sh

Добавление в систему ethX c произвольным MAC

Скрипт создаёт в системе дополнительный (виртуальный) адаптер с произвольным МАС-адресом. Например, в случае если ваш ноутбук не имеет Ethernet-адаптера или в куче других случаев :)

Исключительно для справки: Новые версии FLEXLM могут поддерживать несколько HostID одновременно (не только eth0, но и eth*)

Использование

- Измените под собственные нужны переменные

$DEVи$MACв скриптеfake-nic.sh - Запустите скрипт из под

root-пользователя:

./fake-nic.sh

скрипт установит неодостающие пакеты в вашу систему и добавит сетевой адаптер с заданным $DEV (имя) и $MAC (hostid).

Автовыполнение при загрузке

Небрежный способ поднять сетевой адаптер при каждом старте системы - это добавить в /etc/rc.local следующие строки:

MAC="E4:7D:DE:AD:BE:EF"

DEV="eth1"

ip tuntap add ${DEV} mode tap

ifconfig ${DEV} hw ether ${MAC}

ifconfig ${DEV} up

Ограничения

Работа скрипта проверена в ОС RHEL/CentOS 6.x/7.x. Внутри скрипта встроена авто-проверка запуска именно в этих системах.

Планы

- Передавать DEV и MAC как аргументы командной строки

- Оформить скрипт для запуска из systemd при каждом старте системы

Скрипт

https://github.com/iDoka/eda-scripts/blob/master/fake-nic.sh

Встраивание номера ревизии в битстрим FPGA

Скрипт впечатывает дату сборки и хэш прошивки в образ битстрима FPGA

Использование

На вход передаётся образ в формате mcs и формат выходного файла (intel либо motorola). В утилите настраиваются адреса, по которым располагать дату и хэшсам: для даты отведено 4 байта (время последней модификации файла прошивки в формате линукс - число секунд, отсчитываемые с эпохи) и 16 байт для результата md5sum от содержимого образа файла прошивки.

Зависимости

Скрипт требует установленного и прописанного в PATH ПО Xilinx Lab Tools и пакета srecord.

Скрипт

https://github.com/iDoka/eda-scripts/blob/master/vergen-fpga.sh

Настройки репозитария git для ASIC/FPGA проектов

Скрипт создает пустой реопзитарий с преднастроенными файлами .gitattributes и .gitignore

Использование

Просто набрать в командной строке:

./git-setting.sh /путь/к/будущему/репозитарию

Зависимости

Необходимо установить клиент finger:

yum install -y finger

Планы

- Проверка существования

$GIT_DIR, если не существует - создание - Автоматическое создание типичной для EDA-проектов структуры папок

Скрипт и файлы

- https://github.com/iDoka/eda-scripts/blob/master/git-setting.sh

- https://github.com/iDoka/eda-scripts/tree/master/gitignore

- https://github.com/iDoka/eda-scripts/tree/master/gitattributes

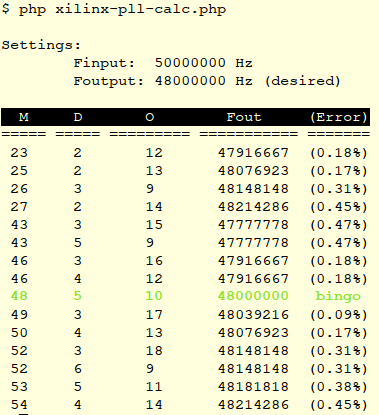

Подбор параметров блока PLL/DCM для Xilinx FPGA

Скрипт печатает таблицу коэффициентов блока ФАПЧ для ПЛИС Xilinx при удовлетворении допуска в % для заданных опорной и выходной частот.

Использование

- Задайте необходимые значения переменным

$F_input(Гц),$F_desired(Гц) и$precission(%) в скриптеxilinx-pll-calc.php - Выберите необходимое семейство ПЛИС, например:

$FPGA = $SPARTAN6; - Запустите скрипт в интерпретаторе:

php xilinx-pll-calc.php

и постарайтесь найти зеленую строку в выводе скрипта:

Ограничения

В настоящий момент скрипт поддерживает следующие семейства ПЛИС Xilinx:

- Xilinx Spartan-6

- Xilinx Virtex-7

- [добавьте сюда своё любимое семейство ПЛИС. см.далее]

Добавление нового семейства ПЛИС

Xilinx, Altera, Lattice?… Тул может быть адаптирован под любого производителя и семейство!

Быстрый путь для добавления нового семейства ПЛИС состоит в заполнении ассоциативного массива (диапазоны мин. и макс. значений частот и коэффициентов берутся из даташита соответствующего семейства):

$VIRTEX7 = array(

"FREQ_INP_MIN" => 19e6,

"FREQ_INP_MAX" => 800e6,

"FREQ_VCO_MIN" => 800e6,

"FREQ_VCO_MAX" => 1600e6,

"FREQ_OUT_MIN" => 6.25e6,

"FREQ_OUT_MAX" => 800e6,

"M_MIN" => 2,

"M_MAX" => 64,

"D_MIN" => 1,

"D_MAX" => 128,

"O_MIN" => 1,

"O_MAX" => 56);

Нижеприведенная формула приоткроет завесу тайны относительно смысла таких переменных как: M, D, O, FREQ_INP, FREQ_VCO, FREQ_OUT.

#######################

######################## #

# # Useful Folmulae #

# M # for PLL Equation #

# Fvco = Fin * - # #

# D #######################

# #

# Fvco M #

# Fout = ---- or Fout = Fin * ----- #

# O D*O #

# #

###########################################

Планы

Реализовать режим сцепки последовательно двух ФАПЧ для реализации недостижимых с помощью одной ФАПЧ условий по выходной частоте.

Скрипт

https://github.com/iDoka/eda-scripts/blob/master/xilinx-pll-calc.php