В докладе затрагивается тема современного железа для построения ускорителей криптографических функций на ПЛИС. На примере конкретных криптоалгоритмов рассматриваются требования к реализации на ПЛИС, затрагиваются особенности реализации. Раскрываются различные методики и подходы по оптимизации криптоакселераторов на FPGA.

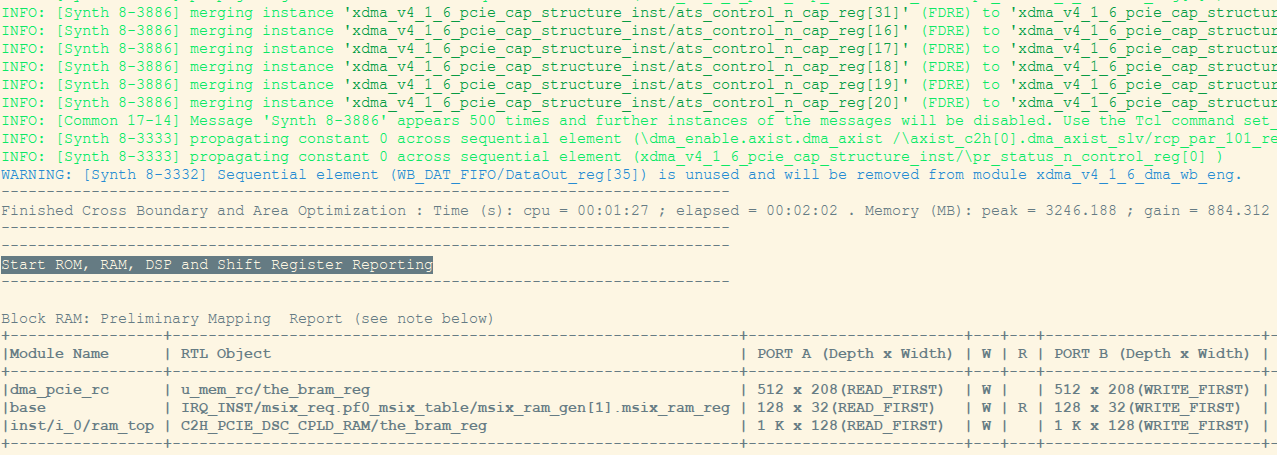

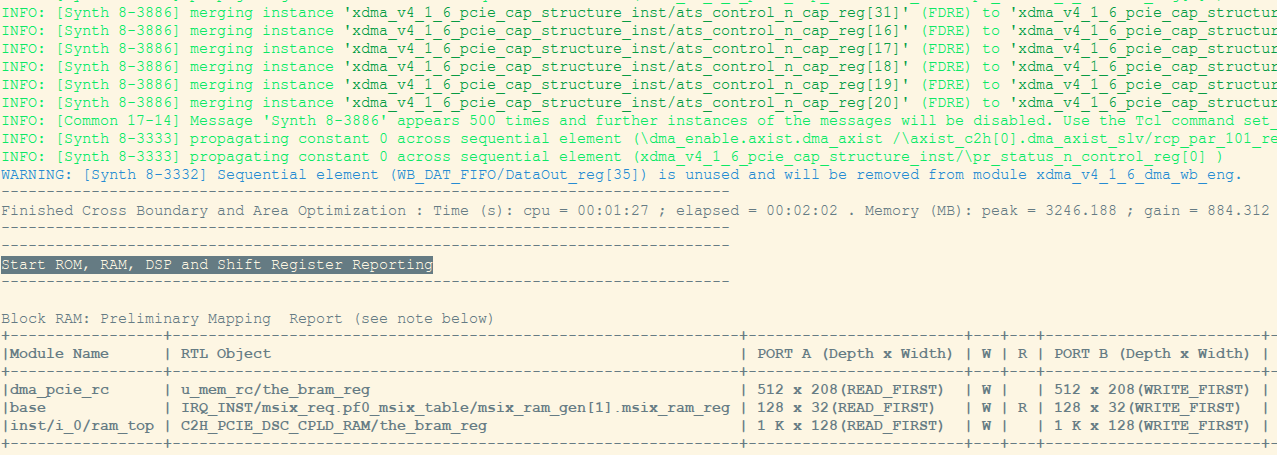

Наконец дошли руки сделать то, что так не хватало в ежедневном рутинном разглядывании серых логов - разукрашку логов вивадо, работающую в рантайм.

Перепробовав некоторое количество вариантов (ccze, awk, multitail), остановился на sed.

Для тех кто давно в теме FPG/A/SIC или просто по работе/хобби связан с проектированием на ПЛИС (или СБИС) удобно под рукой иметь агрегатор полезностей и советов, чем тратить время на самостоятельный сёрфинг по LinkedIn/Twitter/WikiChip/SemiWiki/etc..

Note!: Все команды вводятся в интерпретаторе TCL в интерактивном или пакетном режимах.

Приведенное ниже - описание к коллекции моих EDA-скриптов для работы с тулами для ASIC и FPGA