В докладе затрагивается тема современного железа для построения ускорителей криптографических функций на ПЛИС. На примере конкретных криптоалгоритмов рассматриваются требования к реализации на ПЛИС, затрагиваются особенности реализации. Раскрываются различные методики и подходы по оптимизации криптоакселераторов на FPGA.

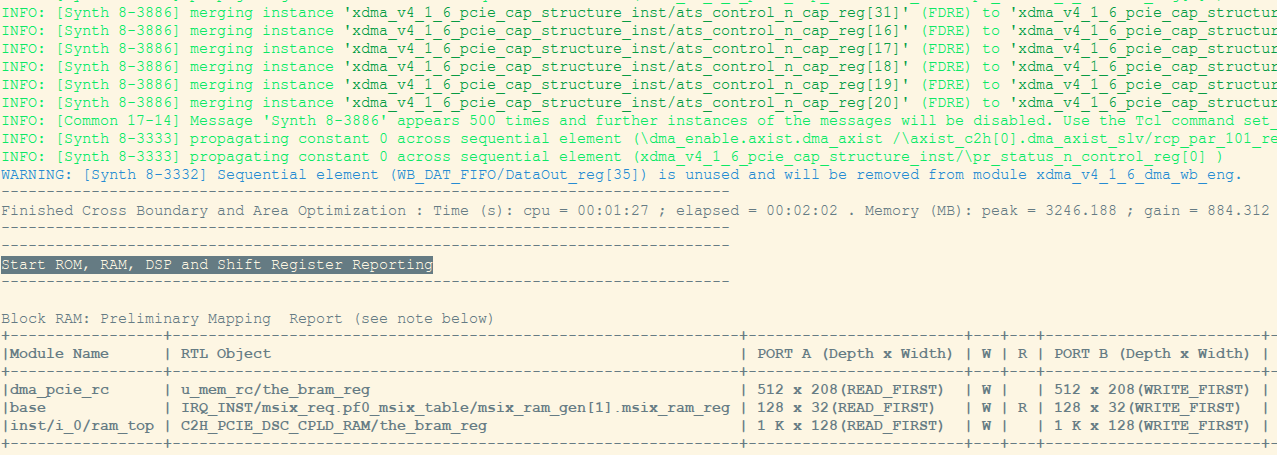

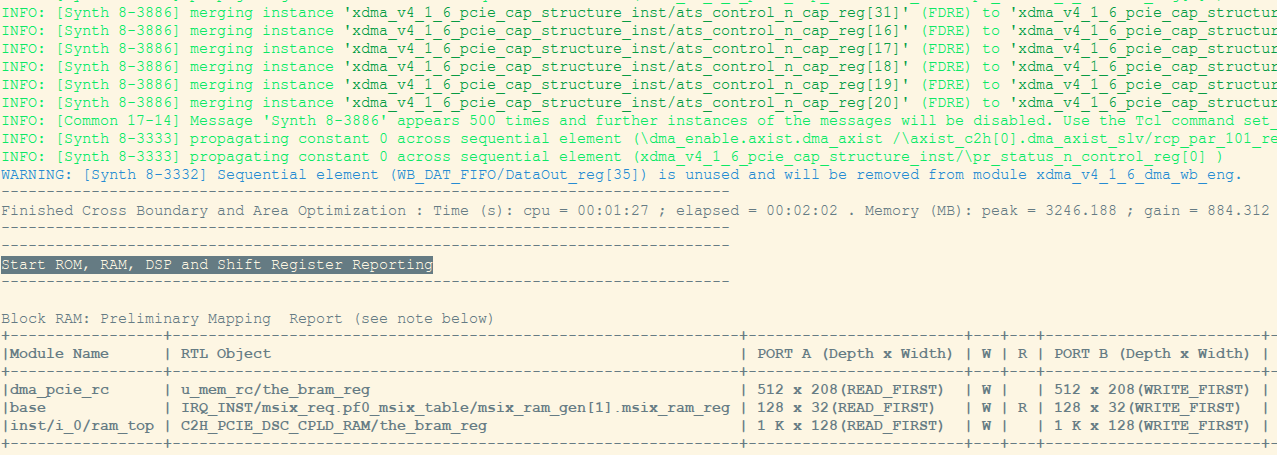

Наконец дошли руки сделать то, что так не хватало в ежедневном рутинном разглядывании серых логов - разукрашку логов вивадо, работающую в рантайм.

Перепробовав некоторое количество вариантов (ccze, awk, multitail), остановился на sed.

Inferring true dual-port, dual-clock RAMs in Xilinx and Altera FPGAs

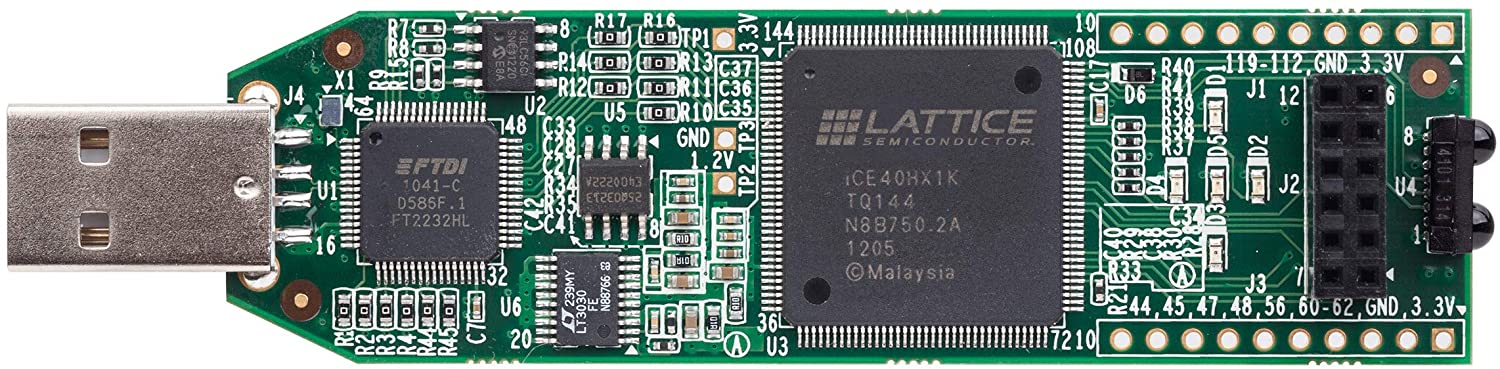

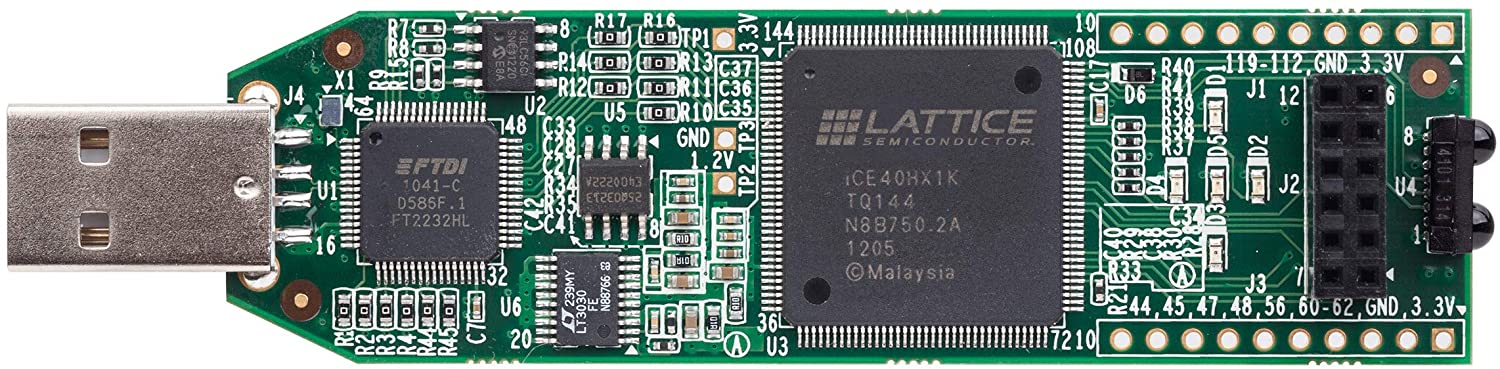

Какой-то тренд в последнее время на выпуск мини-, мико- и даже нано-плат для FPGA, моду тут задал ICEstick от Lattice, но неужели эволюция нас отбросила обратно в нулевые, когда мужчины мерялись телефонами (у кого меньше) ?!..

Более 10ти лет назад когда FPGA были недостаточно большими для одновременного размещения там достаточно жирного IP (ЦОС) и CPU, мы разработали кастомный комбайн для РоС в реальном окружении: