Что это?

Аппаратный (синтезируемый) кодер и декодер самокорректирующихся кодов им.Хэмминга, позволяющих исправлять одиночную ошибку (и находить двойную). Алгоритм коррекции ошибок Хемминга достаточно нетребователен к ресурсам и надёжен; он позволяет значительно повысить надежность передачи и/или хранения данных; также он используется в куче сфер для безотказного функционирования оборудования: отказоустойчивые сервера, аэрокосмическая электроника, радиационно-стойкая элементная база (как альтернатива мажорированию: для защиты RAM и параллельных шин данных).

Возможности

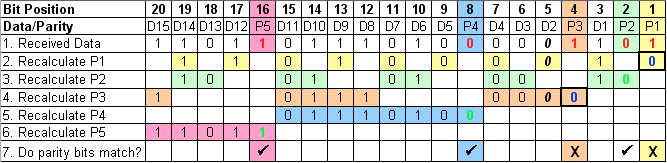

- Шифратор и дешифратор стандартных кодов Хэмминга и кодов с дополнительным битом чётности (т.н. SECDED, который например используется в серверной DRAM: позволяет исправить одну ошибку и обнаружить две)

- Поддерживается запуск в MatLab и GNU Octave (используется функция

hammgen()) - Возможность задавать произвольную разрядность входных данных (переменная

K) - Возможность задавать собственный полином (массив

POLY) - Выходной формат: Verilog HDL 2001

- Полностью комбинационная схема, минимальная latency (добавьте регистровый pipeline по своему вкусу, если гонитесь за макс.частотой работы схемы)

- Сигнал с декодера, индицирующий статус:

- отсутствие ошибки (сбойные биты отсутствуют)

- исправимая ошибка (1 сбойный бит)

- неисправимая ошибка (>1 сбойного бита)

Хотелки

- Прикрутить именование модулей верилога в соответствии с разрядностью входных данных (чтобы в проекте не было конфликта имён из-за возможного использования нескольких модулей для различной разрядности)