Первый вариант заголовка: Bitmine & InnoSilicon: История об одном неудавшемся чипмейкерстве; но порывшись в сети и найдя ответное открытое письмо InnoSilicon, нельзя утверждать, что всё так однозначно в этой истории.

Жил-был такой зарегистрированный в Швейцарии стартап, звался он BITMINE AG, занимался разработкой СБИС для майнинга биткоинов и производством майнеров на базе собственной же СБИС, но что-то не задалось у этого стартапа с бизнесом и в 2015г он объявил себя банкротом (после чего против компании были поданы многочисленные иски), опубликовав на своём сайте https://bitmine.ch/ открытое письмо и указав на основные причины этого, которые заслуживают рассмотрения на мой взгляд. Итак что же или кого же винит BITMINE в собственных неудачах?

Причины банкротства

Заранее отмечу, что нижеперечисленные причины так или иначе являются следствием задержки выхода на рынок в силу различных обстоятельств.

Изменение стоимости биткоина и увеличение сложности добычи

Из-за быстрого увеличения стоимости майнинга и падения стоимости BTC (2014-2015гг) более половины клиентов отменили свои заказы. Компания осознавала эти риски, но слепо верила в силу биткоина и оправдывает свой провал тем, что многие конкуренты так же обанкротились идя на поводу у общей истерии первой криптовалюты.

InnoSilicon

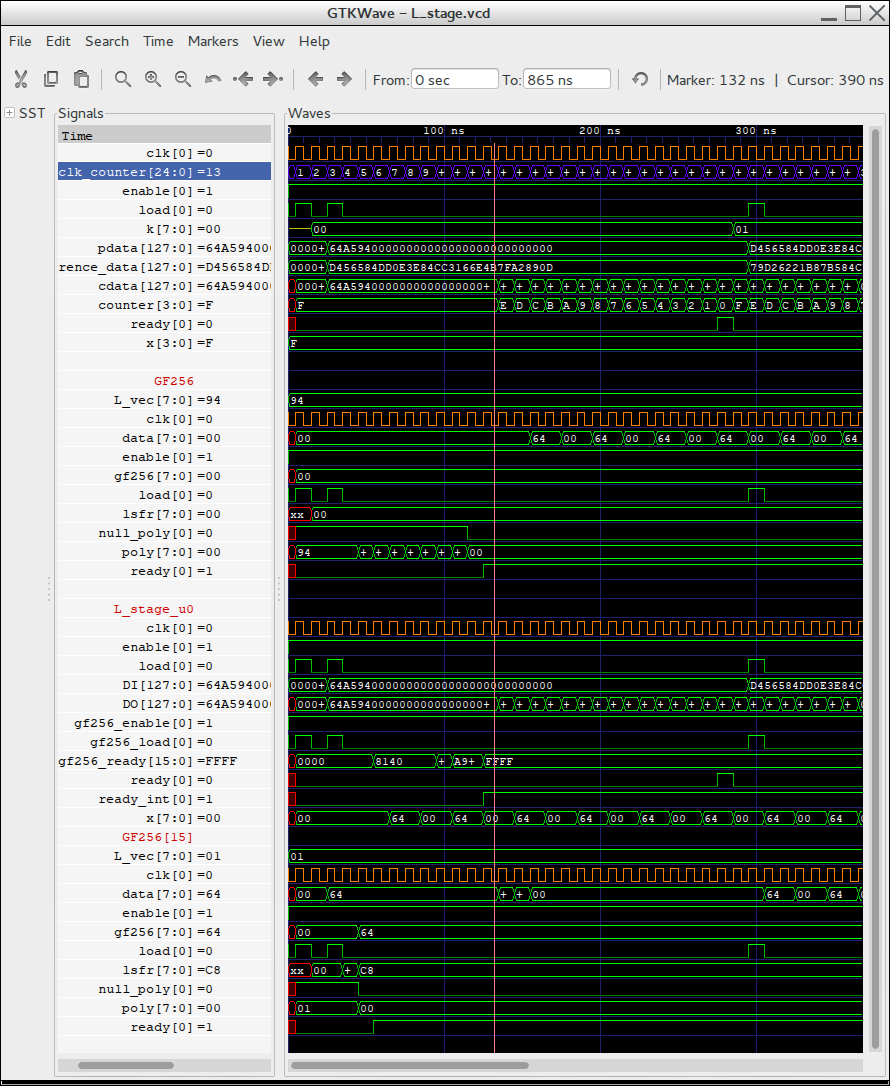

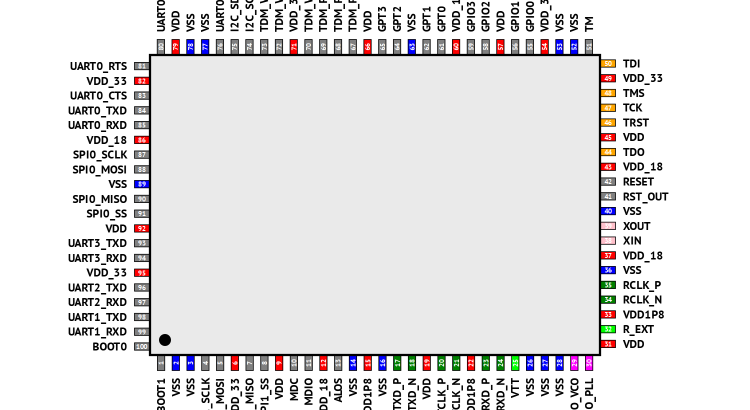

Это основной пункт «оправдательного» письма. InnoSilicon — китайский дизайн-центр; подрядчик и впоследствии партнёр, который отлично подошёл на роль главного козла отпущения. Утверждается, что InnoSilicon на условиях подрядчика занималась разработкой ASIC «под ключ» по технологии 28нм (включая создание топологии, масок, изготовление чипов и корпусирование), используя ноу-хау, предоставленные BITMINE AG. Контракт подряда предусматривал эксклюзивное право Bitmine на продажу чипов А1 сроком на 1 год. Однако, со слов Bitmine, InnoSilicon начала продавать их А1 с самого начала производства на сторону, притом по отпускной цене, ниже, чем они доставались самой Bitmine, которой партии чипов были отгружены с различными задержками, вопреки контракту. Также утверждается, что поскольку большиснтво отгруженных чипов было бракованными, это заставило Bitmine заказывать дополнительные партии чтобы выполнить обязательства перед клиентами, и в итоге InnoSilicon сумело выкачать подобным образом из Bitmine в общей сумме около 8ми миллионов франков (!). Также утверждается, что китайские законы таковы, что Bitmine никогда не смог бы выиграть суд против InnoSilicon.

«Непредвиденные» инженерные сложности

При разработке источников питания для СБИС был допущен просчёт из-за чего возникла необходимость нанять более квалифицированных инженеров и запуска дополнительных (незапланированных) итераций дизайна. Утверждается, что даже новые, более квалифицированные инженеры слишком поздно решили проблему. Вторая часть проблемы — острый дефицит и задержка поставки ключевых компонентов системы питания майнера: контроллеры DC/DC-преобразовтелей, танталовые конденсаторы, MOSFETы, из-за чего серийные изделия не вышли в срок или не вышли вовсе.

Взгляд глазами InnoSilicon

Innosilicon Inc в ответном открытом письме утверждает, что она является действующим и единственным обладателем прав на A1 BTC ASIC и A2 LTC ASIC. Единственными причинами неудачам Bitmine является инженерная некомпетентность и безрассудный бизнес-риск.

1. A1 ASIC вышел вовремя и работоспособным, с типовым для техпроцесса 28нм выходом годных. На момент получения Bitmine чипов А1, рынок ВТС был весьма горячим, но Bitmine не смогли в приемлемые сроки выпустить майнеры на базе чипа А1. Причиной, по которой Bitmine не смогли в срок выпустить майнеры на базе А1, является инженерная некомпетентность и ошибки в проектировании системы питания чипов и многочисленные ошибки в дизайне печатных плат, которые требовали новых итераций и перевыпуска PCB.

2. Начиная с октября 2013 г проект А1 был продолжен на партнерских условиях, из-за неспособности Bitmine в дальнейшем финансировать проект. Тогда же были внесены поправки в контракт, позволяющие Innosilicon продавать чипы А1 на правах, равных с правами Bitmine.

3. Innosilicon единолично разработал и владеет 100% интеллектуальной собственности, использованной в чипе А1. Innosilicon — известный и уважаемый во всём мире дизайн-центр с хорошей репутацией среди заказчиков и превосходным портфолио выполненных проектов. После успеха А1 BTC, Innosilicon разработал и вывел на рынок А2 LTC, а в последствии и А4 LTC, которые быстро стали номер 1 на рынке майнинга. Bitmine — компания, состоящая из двух человек с нулевым опытом в области микроэлектроники и цифрового дизайна. Согласно контракта, любой проектный взнос компании принадлежит компании, сделавшей его. Фактический взнос Bitmine — это файлы тестовых векторов для валидации СБИС.

4. Bitmine использовал деньги своих клиентов из предзаказов, чтобы приобрести себе сторонние фермы майнинга и проводил рискованные операции с биткоинами, на чём и погорел. Реальной проблемой Bitmine являлся посредственный риск-менеджмент и отсутствующая компетенция в технических вопросах на высококонкурентном рынке. У Bitmine было достаточное окно возможности, чтобы разработать дизайн майнера на базе А1, до прихода чипа с фабрики, но они эпично профакапили эту возможность. Даже после выхода майнера на А1 от Bitmine, у него наблюдались проблемы со стабильностью работы, что подтвержлают многочисленные жалобы немногочисленных клиентов.

Выводы для начинающих чипмейкеров

Если правдивы заявления Bitmine

1. IP: Необходимо принимать меры по защите своей интеллектуальной собственности, и я говорю не об юридических гарантиях защиты: требуется предотвратить риск и максимально снизить привлекательность использования вашего продукта без вашего ведома — на сегодня чип без документации по программированию, даташитов с режимами работы и характеристиками, информационных протоколов обмена малопривлекателен для производства в третью смену и отгрузку на сторону (а конечному пользователю, обычно, эти данные не нужны). Концентрируйте на своей стороне контроль за работой чипа, вплоть до параноидальной встройки блока с UID (e-Fuse), который по процедуре инициализации рабочего режима аутентифицируется вашим сервером в интернете (главное не перестараться и соблюсти tradeoff между удобством для клиента и защитой реализованных в кремнии ноу-хау).

2. Аналогичен пп.2 ниже.

Если правдивы заявления Innosilicon

1. Время — деньги: на эти грабли не наступали лишь единицы. собственными глазами был очевидцем нескольких схожих ситуаций. Типичная: торопливость в желании скорого TapeOut оборачивается тем, что сама работа начинается только по приходу чипа (тут был место правда СнК — программисты без малого 2 года возились оживляя кристалл, работая на пополнении Silicon Errata и написании драйверов), хотя идеологически и методологически должна была быть выполнена до отдачи проекта на фабрику. Или другой пример: чип пришёл раньше запланированного срока (есть такая профессия — глотатели чипов), а с ним нельзя начать работы — не готовы PCB, либо ошибки в дизайне и необходима еще одна итерация (перевыпуск) дизайна — а ведь большинство ошибок дизайна можно найти без установки чипа (нам очень повезло что мы живем в эпоху экстремальной доступности измерительного и диагностического оборудования): необходимо только изготовить и смонтировать PCB, чтобы начать отлаживать дизайн в железе (типично, самые частые ошибки как раз в системе питания СБИС).

2. Не продешевите: войско «студентов-ардуинщиков» врядли в принципе в адекватное время и затраты материальных ресурсов решит подводные камни, которые всплывут при процедуре bring-up первых пришедших с фабрики чипов. Необходимо сразу закладывать бюджет на матерого разработчика, лучше по рекомендациям знакомых/коллег по цеху. Да и в целом в руководстве компании стояли гуманитарии менеджеры, рассудочность технических решений которых под большим вопросом, в таких глобальных по финансам проектах как чипмейкерство среди лиц принимающих решение (и/или соучредитель) должен быть как минимум один сильный технический лидер, который понимает технические риски проекта и знает что с ними делать: как на этапах планирования проекта, когда происходит разделение ролей — что оставить у себя, а что можно отдать на подряд, так и на более поздних этапах, при срабатывании триггеров рисков.

3. Риск-менеджмент: как было сказано выше, докучи необходимо учитывать еще и технические риски. Помимо этого стоит отдавать себе отчет в насколько высококонкурентной сфере вы решаете испытать удачу: промедление в выходе на рынок эквивалентно банкротству предприятия (время — деньги) и при задержке в каких-то 2 месяца ваш продукт уже может быть никому не интересен. Также стоит упомянуть, что необходимо отдавать себе отчёт в том, насколько дорогостоящее само по себе занятие чипмейкерством. Bitmine молодцы, что полностью переложили риски по разработке и изготовлению чипа на Innosilicon, а Innosilicon молодцы, что профессионалы своего дела и не облажались. Однако при желании защитить свою интеллектуальную собственность и взять на себя часть технических рисков — будьте готовы иметь соразмерную отрасли подушку безопасности чтобы изыскать возможность перевыпустить маски в случае если первый блин чип будет комом.

Читать далее