В заметке рассмотрим какие же хитрости имплементации необходимо учесть юному (или не очень) чипмейкеру, которому досталась такая привелегия как реализация в кремнии фабрики подсчета хешей для майнинга коинов.

Классифицируем особенности реализации ASIC для майнинга биткоина либо аналогичных криптовалют на несколько категорий (заранее отмечу, что особенности реализации призваны в том или ином виде оптимизировать себестоимость майнинг-чипов и по максимуму поднять удельную (на чип) производительность):

Архитектура

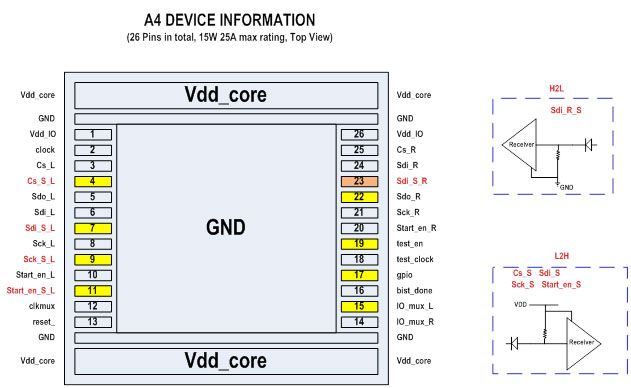

Поскольку современные фермы должны быть масштабируемы, то всегда предусмотрена возможность каскадирования в daisy chain нескольких сотен/тысяч чипов (наиболее распространенный интерфейс для внешних коммуникаций — SPI).

RTL-кодирование

При разработке ASIC-майнеров часто отказываются от верилог-кодирования, отдают предпочтение новомодным метросексуальным JS-фреймворкам, поэтому этот раздел под NDA пустой.

Физический дизайн и топология

Чтобы не облажаться по полной как описано в заметке не стоит отдавать весь физдизайн на аутсорс в дизайн-центр при фабрике, нужен разумный компромисс между рисками разной природы.

Список используемых ухищрений:

- Использование современного техпроцесса, обеспечивающего баланс требований по предельному быстродействию ячеек и их динамическому потреблению (TSMC HPP/HPM/HPC+) — утечки в статике на числодробилке работающей 24/7 мало кого волнуют

- Активное использование технологии DVS (Dynamic Voltage Scaling) для того чтобы у одного и того же ASIC было два профиля тепловыделения: режим максимальной производительности (т.н. турбо) для использования с активным охлаждением и стандартный режим производительности для пассивного охлаждения. Так или иначе это маркетинговые названия не отражающие физическую суть, а суть в том, что turbo — это может быть работа на пониженном Vcore (например, 0.85В вместо стандартных 0.9В для TSMC 28nm), а standart — работа на сверхнизком Vcore (0.78В для TSMC 28нм). Сделано это с целью уложиться в TDP используемых корпусов

- В каких-то экзотических реализациях отказываются от тактовых деревьев и синхронного дизайна в целях уменьшения тепловыделения/потребления

- Из аналоговых блоков используют разве что ФАПЧ для получения высокой частоты тактирования внутри кристалла. Чипы майнера, выполненные по современным технологиям 40..16нм работают на частотах от 1 ГГц и выше, из-за проблем с целостностью цифрового сигнала такую частоту сложно завести на чип снаружи. Пожалуй, в рамках оптимизации стоимости это чуть ли не единственный аналоговый блок, необходимый для дизайна ASIC-майнера.

Корпусирование

Тут две основные тенденции: максимальное удешевление корпусирования и эффективный отвод мощности от кристалла, каким образом этого достигают?

WireBond

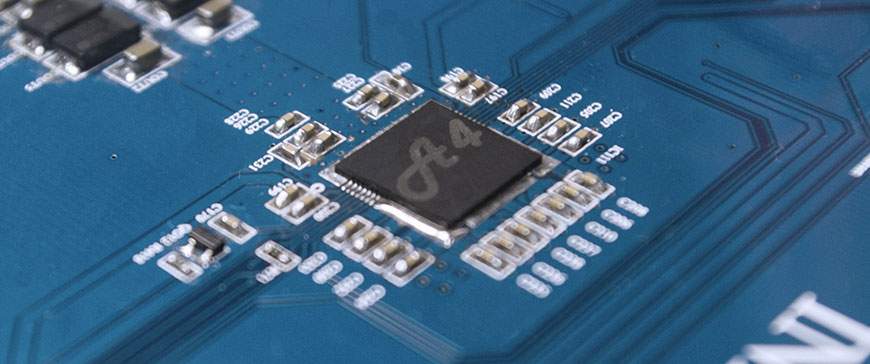

Небольшое число ног и отсутствие высокоскоростных интерфейсов позволяют использовать доступную и недорогую разварку кристалла по технологии WireBond.

Эффективный отвод мощности

Минимальное число ног и тут играет на руку, также как и использование последовательных интерфейсов для коммуникации с фабрикой хеш-блоков. Активно использующиеся массивные lane для ввода питания ядра и земли (для подвода к чипу большого тока с низким падением напряжения) служат и для второй функции: большой пятак земли выполняет еще и важную функцию отвода тепла от кристалла (эти решения очень напомнили мне ноу-хау последного десятилетия от InternationalRectifier в их SMD-корпусостроении MOSFET-ов).

Проектирование на уровне системы и иные ухищрения

Поскольку чип представляет собой достаточно регулярную структуру фабрики блоков по расчету хешсум, то часто разработчики вносят в схему возможность байпаса произвольных блоков и механизм BIST (самотестирования). Это преследует сразу две DFT-цели:

- Экономия на производственном тестировании (поскольку почти всю площадь кристалла занимают блоки расчета хешсумм)

- Увеличение выхода годных (бракованные по результатам самотеста блоки расчета хешсум не используются в работе — в принципе это практически та же самая техника, что используется при тестировании и отбраковке больших массивов накристальной SRAM, только тут еще и на eFuse съэкономили)

Выводы

Как видим, особенностей реализации не так уж и много, однако (экономический) эффект от внедрения не следует недооценивать: специализированные ASIC-чипы для майнинга пережили уже не одно поколение и передовыми компаниями был накоплен некоторый опыт, который и учтён в последнем поколении чипов.