Данный генератор создаёт синтезируемое HDL-описание для аппаратного кодера и декодера кодов коррекции ошибок Хемминга. На выходе получается чисто комбинационный верилог-код, поэтому если кому необходимо пожертвовать задержкой в угоду производительность — вправе добавить на выход столько линеек регистров, сколько требуется для данной разрядности кода (при увеличении разрядности начинает каскадироваться дерево XOR’ов: для ASIC это максимум XOR4, а для FPGA — LUT6). Формат выходного файла соответствует стандарту Verilog-2001. Сфера применения широка: от защиты ECC DRAM в отказоустойчивых серверах до удовлетворения одного из требований автомобильного ISO26262 — защита ECC внутренних шин, ОЗУ и Флеш-памяти.

Возможности

На данный момент генератор позволяет формировать код для кодера/декодера ECC и SECDED (позволяет исправить одну ошибку и обнаружить две).

Декодер имеет выход статуса, по которому можно судить была ли ошибка в принимаемом потоке, а если была — то была ли исправлена.

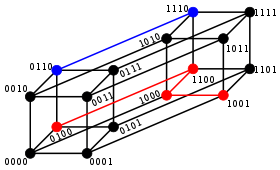

Если вы хотите посмотреть на исходники и понять как же всё это устроено, то тут отличная отправная точка для изучения этого.

Ограничения

На данный момент разрядность входных данных, защищаемых кодом Хемминга может находиться в пределах от 4 до 64 бит. Это искусственное ограничение онлайн-версии (связанное с рациональным использованием процессорного времени на хостинге). Если необходимо работать с шинами большей разрядности — используйте Матлаб/Октав-версию генератора.

Планы

- Добавить кодер Рида-Соломона

- При использовании нескольких кодеров различной разрядности в проекте возможен конфликт имён, поэтому, возможно, стоит вынести обозначение разрядности в имена модулей

Если у Вас есть идеи об улучшении генератора, либо, по вашему мнению, на каком-то наборе данных он демонстрирует некорректную работу, то, пожалуйста, свяжитесь со мной.